9M Pipelined Zero Bus Latency (ZBL) SRAM

(HM66WP18512) 512-Kword × 18-bit (HM66WP36256) 256-Kword × 36-bit

# **HITACHI**

ADE-203-1284D (Z) Preliminary Rev. 0.4 Jun. 21, 2002

### **Description**

The HM66WP18512 is a synchronous fast static RAM organized as 512-Kword  $\times$  18-bit. The HM66WP36256 is a synchronous fast static RAM organized as 256-Kword  $\times$  36-bit. It has realized high speed access time by employing the most advanced CMOS process and high speed circuit designing technology. It is most appropriate for the application which requires high speed, high density memory and wide bit width configuration, such as cache and buffer memory in system. It is packaged in standard 100-pin LQFP.

Note: All power supply  $(V_{DD}, V_{DDQ})$  and ground  $(V_{SS})$  pins must be connected for proper operation of the device.

ZBL: Zero Bus Latency and compatible ZBT<sup>™</sup> SRAM. ZBT<sup>™</sup> is trademark of Integrated Device Technology, Inc.,

#### **Features**

- 3.3 V or 2.5 V power supply, 3.3 V or 2.5 V I/O supply voltage

- Clock frequency: 250/166 MHz

- Fast clock access time: 2.6/3.5 ns (max)

- Low operating current: 250/200 mA (max)

- Address data pipeline capability

- Internal input registers (Address, Data, Control)

- Internal self-timed write cycle

- ADV/LD burst control pins

- Internally synchronized registered outputs eliminate the need to control  $\overline{OE}$

- Individual byte write control

- Power down state via ZZ

- Common data inputs and data outputs

- High board density 100-pin LQFP package

- Burst control selected pin LBO (Interleave or linear burst order)

Preliminary: The specifications of this device are subject to change without notice. Please contact your nearest Hitachi's Sales Dept. regarding specifications.

# **Ordering Information**

| Type No.         | Access time | CPU clock rate | Package                |

|------------------|-------------|----------------|------------------------|

| HM66WP18512FP-40 | 2.6 ns      | 250 MHz        | LQFP 100-pin (FP-100H) |

| HM66WP18512FP-60 | 3.5 ns      | 166 MHz        |                        |

| HM66WP36256FP-40 | 2.6 ns      | 250 MHz        | _                      |

| HM66WP36256FP-60 | 3.5 ns      | 166 MHz        |                        |

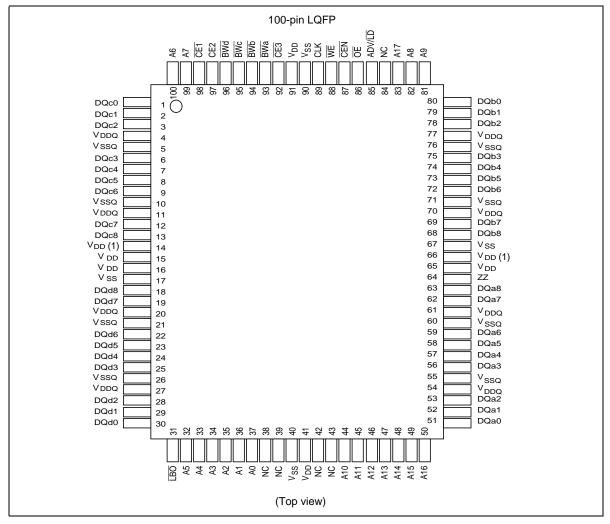

### Pin Arrangement (HM66WP36256) 100PIN-LQFP

Note: Pins 14 and 66 are not  $V_{\scriptscriptstyle DD}$  Supply, but have to be connected  $V_{\scriptscriptstyle DD}$ .

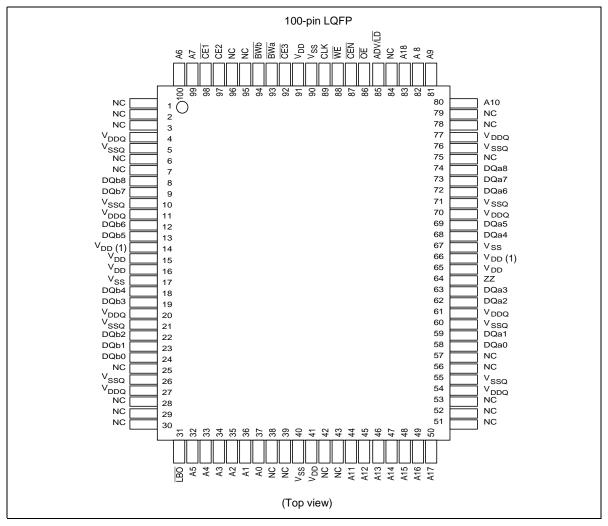

### Pin Arrangement (HM66WP18512) 100PIN-LQFP

Note: Pins 14 and 66 are not  $V_{\rm DD}$  Supply, but have to be connected  $V_{\rm DD}$ .

# Pin Description (See Detailed Pin Description)

|                                   | I/O type     | Description                                                            | Notes                           |

|-----------------------------------|--------------|------------------------------------------------------------------------|---------------------------------|

| A0, A1 and A2-17<br>(HM66WP36256) | Input        | 18 address inputs                                                      |                                 |

| A0, A1 and A2-18<br>(HM66WP18512) | Input        | 19 address inputs                                                      |                                 |

| BWm                               | Input        | Byte write enables BWa controls DQa0 to DQa8 BWb controls DQb0 to DQb8 | m = a, b, c, d<br>(HM66WP36256) |

|                                   |              | BWc controls DQc0 to DQc8 BWd controls DQd0 to DQd8                    | m = a, b<br>(HM66WP18512)       |

| WE                                | Input        | Write enable                                                           |                                 |

| CLK                               | Input        | Clock                                                                  |                                 |

| CE1, CE3, CE2                     | Input        | Chip enable                                                            |                                 |

| ŌĒ                                | Input        | Output enable                                                          |                                 |

| ADV/LD                            | Input        | Address load control                                                   |                                 |

| CEN                               | Input        | Clock enable control                                                   |                                 |

| ZZ                                | Input        | Power down                                                             |                                 |

| LBO                               | Input        | Burst mode control                                                     |                                 |

| NC                                | _            | No connection                                                          |                                 |

| DQmn<br>n = 0 - 8                 | Input/Output | Data input/output                                                      | m = a, b, c, d<br>(HM66WP36256) |

|                                   |              |                                                                        | m = a, b<br>(HM66WP18512)       |

| $V_{DD}$                          | Supply       | Power supply                                                           |                                 |

| $V_{\tiny DDQ}$                   | Supply       | I/O power supply                                                       |                                 |

| V <sub>ss</sub>                   | Supply       | Ground                                                                 |                                 |

# **Detailed Pin Description**

| Pin number(s)<br>LQFP                                 | Symbol                             | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------|------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35, 34, 33, 32,<br>44, 45, 46, 47,<br>48, 49, 50, 81, | ( $\times$ 36-bit $\times$ 18-bit  | Input | Synchronous address inputs: These inputs are registered and must meet setup and hold times around the rising edge of CLK.                                                                                                                                                                                                                                                                                          |

| 82, 83, 99, 100                                       | •                                  |       | Burst address inputs                                                                                                                                                                                                                                                                                                                                                                                               |

| 37, 36                                                | A0, A1                             | _     |                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 80                                                    | A (× 18-bit)                       |       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 93, 94,<br>95, 96                                     | BWa, BWb<br>BWc, BWd<br>(× 36-bit) | Input | Synchronous byte write enables: These active LOW inputs allow individual bytes to be written and must meet the setup and hold times around the rising edge of CLK. A byte write enable is LOW for a WRITE cycle and HIGH for a READ cycle. BWa controls DQa0 to DQa8. BWb controls DQb0 to DQb8. BWc controls DQc0 to DQc8. BWd controls DQd0 to DQd8. Data I/O are tristated if any of these four inputs are LOW. |

| 93, 94                                                | BWa, BWb<br>(× 18-bit)             | _     |                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 87                                                    | CEN                                | Input | Synchronous clock enable: This active LOW internal clock signal is active.                                                                                                                                                                                                                                                                                                                                         |

| 88                                                    | WE                                 | Input | Synchronous write enable: This active LOW input permits write operations and must meet the setup and hold times around the rising edge of CLK.                                                                                                                                                                                                                                                                     |

| 89                                                    | CLK                                | Input | Clock: This signal latches the address, data, chip enables, byte write enables and burst control inputs on its rising edge. All synchronous inputs must meet setup and hold times around the clock's rising edge.                                                                                                                                                                                                  |

| 98                                                    | CE1                                | Input | Synchronous chip enable: This active LOW input is used to enable the device. This input is sampled only when an external address is loaded. This input can be used for memory depth expansion.                                                                                                                                                                                                                     |

| 92                                                    | CE3                                | Input | _                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 97                                                    | CE2                                | Input | Synchronous chip enable: This active HIGH input is used to enable the device. This input sampled only when a new external address is load. This input can be used for memory depth expansion.                                                                                                                                                                                                                      |

| 86                                                    | ŌĒ                                 | Input | Output enable: This active LOW asynchronous input enables the data I/O output drivers.                                                                                                                                                                                                                                                                                                                             |

| 85                                                    | ADV/LD                             | Input | Synchronous address advance or load control: This active HIGH input is used to advance the internal burst counter, controlling burst access after the external address is loaded. A LOW input is caused a new external address to be latched.                                                                                                                                                                      |

# **Detailed Pin Description** (cont)

| Pin number(s)<br>LQFP                                                                            | Symbol                                      | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------|---------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38, 39, 42, 43, 84,                                                                              | NC<br>(× 36-bit)                            | _                | No Connect: These signals are internally not connected.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1, 2, 3, 6, 7, 25, 28, 29, 30, 38, 39, 42, 43, 51, 52, 53, 56, 57, 75, 78, 79, 84, 95, 96        | NC<br>(× 18-bit)                            | _                | No Connect: These signals are internally not connected.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 51, 52, 53, 56, 57, 58, 59, 62, 63, 68, 69, 72,                                                  | DQmn<br>m = a, b,                           | Input/<br>Output | SRAM data I/O: Byte a is DQa0 to DQa8; Byte b is DQb0 to DQb8; Byte c is DQc0 to DQc8; Byte d is DQd0 to DQd8.                                                                                                                                                                                                                                                                                                                                                         |

| 73, 74, 75, 78, 79, 80,<br>1, 2, 3, 6, 7, 8, 9, 12,<br>13, 18, 19, 22, 23, 24,<br>25, 28, 29, 30 | c, d<br>n = 0 - 8<br>(× 36-bit)             |                  | Input data must meet setup and hold times around the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                                                               |

| 58, 59, 62, 63, 68, 69, 72, 73, 74, 8, 9, 12, 13, 18, 19, 22, 23, 24                             | DQmn<br>m = a, b<br>n = 0 - 8<br>(× 18-bit) | Input/<br>Output | SRAM data I/O: Byte a is DQa0 to DQa8; Byte b is DQb0 to DQb8. Input data must meet setup and hold times around the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                |

| 14, 15, 16, 41, 65,<br>66, 91                                                                    | $V_{DD}$                                    | Supply           | Power supply: 3.3 V (+5%/–5%) or 2.5 V (+5%/–5%)                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4, 11, 20, 27, 54<br>61, 70, 77                                                                  | V <sub>DDQ</sub>                            | Supply           | I/O power supply:<br>3.3 V (+5%/–5%)<br>or 2.5 V (+5%/–5%)                                                                                                                                                                                                                                                                                                                                                                                                             |

| 17, 40, 67, 90, 5, 10, 21<br>26, 55, 60, 71, 76                                                  | , V <sub>ss</sub>                           | Supply           | Ground: GND                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 64                                                                                               | ZZ                                          | Input            | Asynchronous power-down (Snooze): This active HIGH input enables SRAM to enter a power-down (Snooze) state with data retention. During Snooze state, data retention is guaranteed. At this time, internal state of the SRAM is not preserved. After Snooze state, SRAM must be initiated with $\overline{\text{CEN}}$ or $\text{ADV}/\overline{\text{LD}}$ using a new external address. This pin must be connected to $V_{ss}$ in systems that do not use ZZ feature. |

| 31                                                                                               | LBO                                         | Input            | Burst order (Interleave burst or linear burst) select pin (DC) This pin must connect $V_{\rm DD}$ or $V_{\rm DDQ}$ or $V_{\rm SS}$ .                                                                                                                                                                                                                                                                                                                                   |

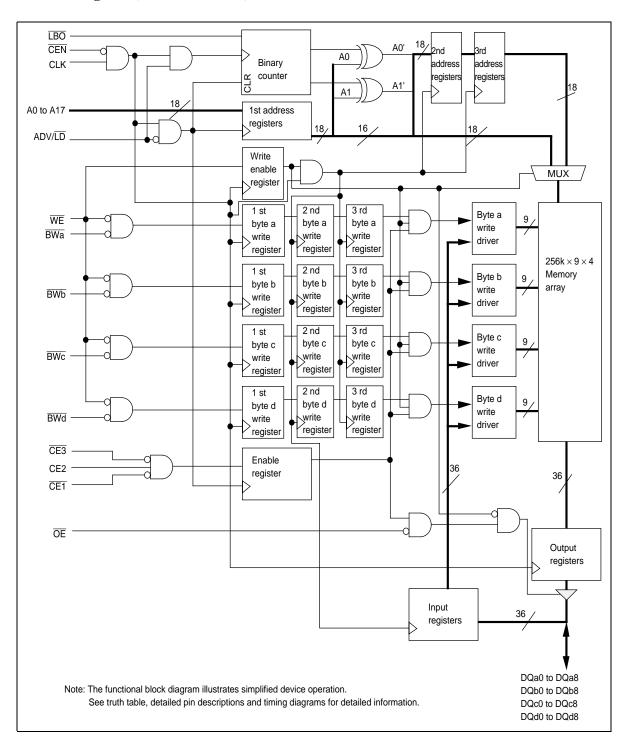

## Block Diagram (HM66WP36256)

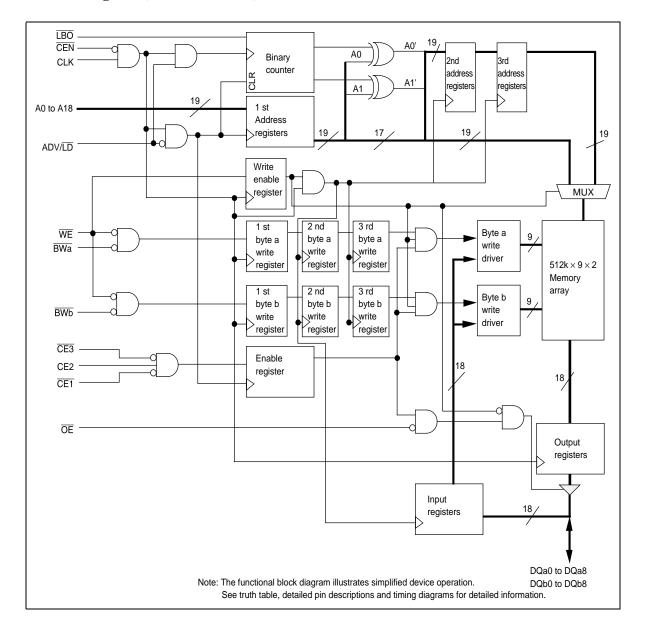

## Block Diagram (HM66WP18512)

#### **Synchronous Truth Table**

|                                  |          |     |     |     | AD۷ | //  |    |     |    |     |        |

|----------------------------------|----------|-----|-----|-----|-----|-----|----|-----|----|-----|--------|

| Operation                        | Address  | CE1 | CE3 | CE2 | LD  | CEN | WE | BWn | OE | CLK | DQ     |

| Deselected cycle, power-down     | None     | Н   | ×   | ×   | L   | L   | ×  | ×   | ×  | L-H | High-Z |

| Deselected cycle, power-down     | None     | ×   | Н   | ×   | L   | L   | ×  | ×   | ×  | L-H | High-Z |

| Deselected cycle, power-down     | None     | ×   | ×   | L   | L   | L   | ×  | ×   | ×  | L-H | High-Z |

| WRITE cycle, begin burst         | External | L   | L   | Н   | L   | L   | L  | L   | ×  | L-H | D      |

| NOP/WRITE Abort, begin burst     | External | L   | L   | Н   | L   | L   | L  | Н   | ×  | L-H | High-Z |

| READ cycle, begin burst          | External | L   | L   | Н   | L   | L   | Н  | ×   | L  | L-H | Q      |

| Dummy READ cycle, begin burst    | External | L   | L   | Н   | L   | L   | Н  | ×   | Н  | L-H | High-Z |

| WRITE cycle, continue burst      | Next     | ×   | ×   | ×   | Н   | L   | ×  | L   | ×  | L-H | D      |

| WRITE Abort, continue burst      | Next     | ×   | ×   | ×   | Н   | L   | ×  | Н   | ×  | L-H | High-Z |

| READ cycle, continue burst       | Next     | ×   | ×   | ×   | Н   | L   | ×  | ×   | L  | L-H | Q      |

| Dummy READ cycle, continue burst | Next     | ×   | ×   | ×   | Н   | L   | ×  | ×   | Н  | L-H | High-Z |

| WRITE cycle, suspend             | Current  | ×   | ×   | ×   | ×   | Н   | ×  | ×   | ×  | L-H | -      |

| READ cycle, suspend              | Current  | ×   | ×   | ×   | ×   | Н   | ×  | ×   | L  | L-H | Q      |

| Dummy READ cycle, suspend        | Current  | ×   | ×   | ×   | ×   | Н   | ×  | ×   | Н  | L-H | High-Z |

Notes: 1. H means logic HIGH, L means logic LOW. × means H or L. BWm = L means any one or more byte write enable signals (BWa, BWb, BWc or BWd) are LOW. BWm = H means all byte write enable signals are HIGH.

- BWa enables write to Bytea (DQa0 to DQa8). BWb enables write to Byteb (DQb0 to DQb8).

BWc enables write to Bytec (DQc0 to DQc8). BWd enables write to Byted (DQd0 to DQd8).

- 3. All inputs except  $\overline{\text{OE}}$  and ZZ must meet setup and hold times around the rising edge (LOW to HIGH) of CLK.

- 4. A WRITE is performed by setting one or more byte write enable signals and WE LOW for the subsequent L-H edge of CLK. Refer to WRITE timing diagram for clarification.

- 5. The status for DQ described in this synchronous truth table appears two clocks after the cycle in which the Read or Write command is asserted.

- 6. If ADV/LD is sampled High that it is continue burst cycle follows before the operation cycle.

- 7. Wait states are inserted by  $\overline{\text{CEN}}$  = High. When  $\overline{\text{CEN}}$  is sampled High after Read cycle, the Read data is maintain as output data. When  $\overline{\text{CEN}}$  is sampled High after Write cycle, the Write Input Data is ignored and is maintained High-Z. Refer to Timing diagram for clarification.

## **Asynchronous Truth Table**

| Operation           | ZZ | ŌĒ | I/O status      |

|---------------------|----|----|-----------------|

| Read                | L  | L  | Data out        |

| Read                | L  | Н  | High-Z          |

| Write               | L  | ×  | High-Z, Data in |

| Deselect            | L  | ×  | High-Z          |

| Power down (Snooze) | Н  | ×  | High-Z          |

Note: H means logic HIGH. L means logic LOW. × means H or L.

#### **Partial Truth Table for Writes**

| Operation       | WE | BWa | BWb | BWc | BWd |

|-----------------|----|-----|-----|-----|-----|

| Read            | Н  | ×   | ×   | ×   | ×   |

| No write        | L  | Н   | Н   | Н   | Н   |

| Write byte a    | L  | L   | Н   | Н   | Н   |

| Write all bytes | L  | L   | L   | L   | L   |

Note: H means logic HIGH. L means logic LOW. × means H or L.

## **Interleave Sequence Table** ( $\overline{LBO} = V_{DD}$ or $V_{DDO}$ )

| Parameter            | Sequence 1 (A1, A0) | Sequence 2 (A1, A0) | Sequence 3 (A1, A0) | Sequence 4<br>(A1, A0) |

|----------------------|---------------------|---------------------|---------------------|------------------------|

| External address     | 0 0                 | 0 1                 | 1 0                 | 1 1                    |

| 1st internal address | 0 1                 | 0 0                 | 1 1                 | 1 0                    |

| 2nd internal address | 1 0                 | 1 1                 | 0 0                 | 0 1                    |

| 3rd internal address | 1 1                 | 1 0                 | 0 1                 | 0 0                    |

Note: Each sequence wraps around to its initial state upon completion.

# **Linear Sequence Table** $(\overline{LBO} = V_{ss})$

| Parameter            | Sequence 1 (A1, A0) | Sequence 2<br>(A1, A0) | Sequence 3 (A1, A0) | Sequence 4<br>(A1, A0) |

|----------------------|---------------------|------------------------|---------------------|------------------------|

| External address     | 0 0                 | 0 1                    | 1 0                 | 1 1                    |

| 1st internal address | 0 1                 | 1 0                    | 11                  | 0 0                    |

| 2nd internal address | 1 0                 | 1 1                    | 0 0                 | 0 1                    |

| 3rd internal address | 11                  | 0 0                    | 0 1                 | 1 0                    |

Note: Each sequence wraps around to its initial state upon completion.

## **Absolute Maximum Ratings**

| Parameter                                    |          | Symbol          | Value                          | Unit |

|----------------------------------------------|----------|-----------------|--------------------------------|------|

| Supply voltage                               |          | V <sub>DD</sub> | -0.5 to +4.6                   | V    |

| Voltage on any pins relative to $V_{\rm ss}$ | (DQ)     | V <sub>T</sub>  | -0.5 to V <sub>DDQ</sub> + 0.5 | V    |

| Except V <sub>DD</sub>                       | (Others) | V <sub>T</sub>  | $-0.5$ to $V_{DD} + 0.5$       | V    |

| Power dissipation                            |          | P <sub>T</sub>  | 1.6                            | W    |

| Operating temperature                        |          | Topr            | 0 to +70                       | °C   |

| Storage temperature range (with bia          | s)       | Tstg (bias)     | -10 to +85                     | °C   |

| Storage temperature range                    |          | Tstg            | -55 to +125                    | °C   |

### **Recommended DC Operating Conditions (3.3V Power supply)**

$(Ta = 0 \text{ to } +70^{\circ}C)$

| Parameter                         |            | Symbol           | Min   | Тур | Max                    | Unit | Note |

|-----------------------------------|------------|------------------|-------|-----|------------------------|------|------|

| Supply voltage (Operating voltage | age range) | V <sub>DD</sub>  | 3.135 | 3.3 | 3.465                  | V    |      |

| Supply I/O voltage (3.3 V I/O)    |            | V <sub>DDQ</sub> | 3.135 | 3.3 | 3.465                  | V    |      |

| Supply I/O voltage (2.5 V I/O)    |            | V <sub>DDQ</sub> | 2.375 | 2.5 | 2.625                  | V    |      |

| Supply voltage to V <sub>ss</sub> |            | V <sub>ss</sub>  | 0.0   | 0.0 | 0.0                    | V    |      |

| Input high voltage (3.3 V I/O)    | (DQ)       | V <sub>IH</sub>  | 2.0   | -   | V <sub>DDQ</sub> + 0.3 | V    |      |

|                                   | (Others)   | V <sub>IH</sub>  | 2.0   | -   | V <sub>DD</sub> + 0.3  | V    |      |

| Input high voltage (2.5 V I/O)    | (DQ)       | V <sub>IH</sub>  | 1.7   | -   | V <sub>DDQ</sub> + 0.3 | V    |      |

|                                   | (Others)   | V <sub>IH</sub>  | 1.7   | -   | V <sub>DD</sub> + 0.3  | V    |      |

| Input low voltage (3.3 V I/O)     |            | V <sub>IL</sub>  | -0.3  | -   | 0.8                    | V    | 1    |

| Input low voltage (2.5 V I/O)     |            | V <sub>IL</sub>  | -0.3  | -   | 0.7                    | V    | 1    |

Note: 1. -2.0 V for undershoot pulse width  $\leq 20\% \ t_{\text{cyc}}$ .

## **Recommended DC Operating Conditions (2.5V Power supply)**

$(Ta = 0 \text{ to } +70^{\circ}C)$

| Parameter                                |          | Symbol           | Min   | Тур | Max                    | Unit | Note |

|------------------------------------------|----------|------------------|-------|-----|------------------------|------|------|

| Supply voltage (Operating voltage range) |          | V <sub>DD</sub>  | 2.375 | 2.5 | 2.625                  | V    |      |

| Supply I/O voltage (2.5 V I/O)           |          | V <sub>DDQ</sub> | 2.375 | 2.5 | 2.625                  | V    |      |

| Supply voltage to V <sub>ss</sub>        |          | V <sub>ss</sub>  | 0.0   | 0.0 | 0.0                    | V    |      |

| Input high voltage (2.5 V I/O)           | (DQ)     | V <sub>IH</sub>  | 1.7   | -   | V <sub>DDQ</sub> + 0.3 | V    |      |

|                                          | (Others) | V <sub>IH</sub>  | 1.7   | -   | V <sub>DD</sub> + 0.3  | V    |      |

| Input low voltage (2.5 V I/O)            |          | V <sub>IL</sub>  | -0.3  | -   | 0.7                    | V    | 1    |

Note: 1. -2.0 V for undershoot pulse width  $\leq 20\% \text{ t}_{\text{cyc}}$ .

## **DC** Characteristics

(Ta = 0 to +70°C,  $V_{_{DD}}$  = 3.3 V +5%/–5% or 2.5 V +5%/–5%)

#### HM66WP18512/HM66WP36256

|                                 | Symbol            | -40        |     | -60        |     |      |                                                                                                                                                                |  |  |

|---------------------------------|-------------------|------------|-----|------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameter                       |                   | Min        | Max | Min        | Max | Unit | Test conditions                                                                                                                                                |  |  |

| Input leakage current           | I <sub>LI</sub>   | -2         | 2   | -2         | 2   | μΑ   | All inputs $Vin = V_{SS} to V_{DD}$                                                                                                                            |  |  |

| Output leakage current          | I <sub>LO</sub>   | <b>-</b> 5 | 5   | <b>-</b> 5 | 5   | μΑ   | $\overline{OE} = V_{IH}$ , $Vout = V_{SS}$ to $V_{DDQ}$                                                                                                        |  |  |

| Operating current               | l <sub>DD</sub>   |            | 250 | _          | 200 | mA   | Device selected, lout = 0 mA, all inputs = $V_{IH}$ or $V_{IL}$ , cycle time = $t_{CYC}$ min.                                                                  |  |  |

| Standby current                 | I <sub>SB</sub>   | _          | 100 | _          | 80  | mA   | Device deselected all inputs = fixed and all inputs $\geq$ V <sub>DD</sub> - 0.2 V or $\leq$ 0.2 V, cycle time = $t_{\text{cyc}}$ min.                         |  |  |

|                                 | I <sub>SB1</sub>  | _          | 30  | _          | 30  | mA   | Device deselected all inputs = fixed and all inputs $\geq V_{DD} - 0.2 \text{ V or } \leq 0.2 \text{ V},$ Frequency = 0 MHz.                                   |  |  |

|                                 | I <sub>SBZZ</sub> | _          | 10  | _          | 10  | mA   | Device deselected all inputs = fixed and all inputs $\geq V_{DD} - 0.2 \text{ V or } \leq 0.2 \text{ V},$ $ZZ \geq V_{DD} - 0.2 \text{ V},$ Frequency = 0 MHz. |  |  |

| Output low voltage (3.3 V I/O)  | V <sub>oL</sub>   | _          | 0.4 | _          | 0.4 | V    | I <sub>OL</sub> = 8 mA                                                                                                                                         |  |  |

| Output high voltage (3.3 V I/O) | V <sub>OH</sub>   | 2.4        | _   | 2.4        | _   | V    | I <sub>OH</sub> = -4 mA                                                                                                                                        |  |  |

| Output low voltage (2.5 V I/O)  | $V_{oL}$          | _          | 0.4 | _          | 0.4 | V    | I <sub>OL</sub> = 1 mA                                                                                                                                         |  |  |

| Output high voltage (2.5 V I/O) | $V_{\text{OH}}$   | 2.0        | _   | 2.0        | _   | V    | I <sub>OH</sub> = -1 mA                                                                                                                                        |  |  |

|                                 |                   |            |     |            |     |      |                                                                                                                                                                |  |  |

## Capacitance

$(Ta=+25^{\circ}C,\,f=1.0$  MHz,  $V_{_{DD}}\!=3.3$  V and  $\,2.5$  V)

| Parameter                | Symbol           | Min | Тур | Max | Unit | Note |

|--------------------------|------------------|-----|-----|-----|------|------|

| Input capacitance        | Cin              | _   | 4   | 5   | pF   | 1    |

| Input/output capacitance | C <sub>I/O</sub> | _   | 6   | 7   | pF   | 1    |

Note: 1. This parameter is sampled and not 100% tested.

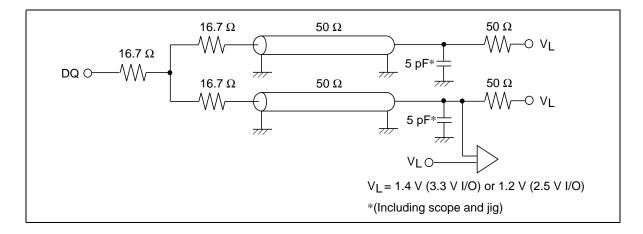

### **AC Characteristics**

$(Ta = 0 \text{ to } +70^{\circ}\text{C}, V_{DD} = 3.3 \text{ V} +5\%/-5\% \text{ and } 2.5 \text{ V} +5\%/-5\%, V_{SS} = 0 \text{ V})$

#### **Test Conditions**

• Input timing measurement reference level :1.4 V (3.3 V I/O)

:1.2 V (2.5 V I/O)

• Input pulse levels: 0 V to 2.8 V (3.3 V I/O)

: 0 V to 2.4 V (2.5 V I/O)

• Input rise and fall time: 2 V/ns (10% - 90%)

• Output timing reference level: 1.4 V (3.3 V I/O)

: 1.2 V (2.5 V I/O)

• Output load: See figure

|                                                                                                                                                                                                                                       |                                                                                   | HM66WP18512/HM66WP36256                                                                                                                                                                                   |     |     |     |     |       |       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-------|-------|

|                                                                                                                                                                                                                                       | Symbol                                                                            |                                                                                                                                                                                                           | -40 |     | -60 |     | _     |       |

| Parameter                                                                                                                                                                                                                             | Standard                                                                          | Alternate                                                                                                                                                                                                 | Min | Max | Min | Max | Unit  | Notes |

| Cycle time                                                                                                                                                                                                                            | t <sub>кнкн</sub>                                                                 | t <sub>cyc</sub>                                                                                                                                                                                          | 4.0 | _   | 6.0 | _   | ns    |       |

| Clock access time                                                                                                                                                                                                                     | t <sub>KHQV</sub>                                                                 | t <sub>CA</sub>                                                                                                                                                                                           | _   | 2.6 | _   | 3.5 | ns    |       |

| Output enable to output valid                                                                                                                                                                                                         | t <sub>GLQV</sub>                                                                 | t <sub>oe</sub>                                                                                                                                                                                           | _   | 2.6 | _   | 3.5 | ns    |       |

| Clock high to output active                                                                                                                                                                                                           | t <sub>KHQX2</sub>                                                                | t <sub>CLZ</sub>                                                                                                                                                                                          | 8.0 | _   | 1.5 | _   | ns    | 1     |

| Clock high to output change                                                                                                                                                                                                           | t <sub>KHQX</sub>                                                                 | t <sub>coн</sub>                                                                                                                                                                                          | 8.0 | _   | 1.5 |     | ns    |       |

| Output enable to output active                                                                                                                                                                                                        | t <sub>GLQX</sub>                                                                 | t <sub>oLZ</sub>                                                                                                                                                                                          | 0   | _   | 0   | _   | ns    | 1     |

| Output disable to Q High-Z                                                                                                                                                                                                            | t <sub>GHQZ</sub>                                                                 | t <sub>ohz</sub>                                                                                                                                                                                          | _   | 2.6 | _   | 3.5 | ns    | 1     |

| Clock high to Q High-Z                                                                                                                                                                                                                | t <sub>KHQZ</sub>                                                                 | t <sub>CHZ</sub>                                                                                                                                                                                          | _   | 2.6 | _   | 3.5 | ns    | 1     |

| Clock high pulse width                                                                                                                                                                                                                | t <sub>KHKL</sub>                                                                 | t <sub>ch</sub>                                                                                                                                                                                           | 1.7 | _   | 2.2 | _   | ns    |       |

| Clock low pulse width                                                                                                                                                                                                                 | t <sub>KLKH</sub>                                                                 | t <sub>cL</sub>                                                                                                                                                                                           | 1.7 | _   | 2.2 | _   | ns    |       |

| Setup Times:     Address     Clock Enable     Input Data     Write (WE, BWa-d)     Address Advance     Chip Enable  Hold Times:     Address     Clock Enable     Input Data     Write (WE, BWa-d)     Address Advance     Chip Enable | tankh tcenvkh tdukh twykh tadvvk tevkh  tkhax tkhax tkhax tkhax tkhax tkhax tkhax | t <sub>SA</sub> t <sub>SCEN</sub> t <sub>SD</sub> t <sub>SW</sub> t <sub>SADV</sub> t <sub>SCE</sub> t <sub>HA</sub> t <sub>HCEN</sub> t <sub>HD</sub> t <sub>HW</sub> t <sub>HADV</sub> t <sub>HCE</sub> | 0.3 | _   | 0.5 | _   | ns    |       |

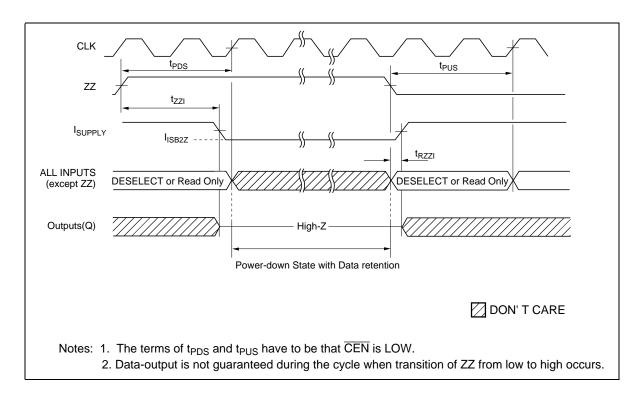

| ZZ Active to input ignored                                                                                                                                                                                                            | -KHEX                                                                             | t <sub>PDS</sub>                                                                                                                                                                                          | 2   |     | 2   |     | cycle | 4     |

| ZZ Inactive to input Sampled                                                                                                                                                                                                          |                                                                                   | t <sub>PUS</sub>                                                                                                                                                                                          | 2   | _   | 2   | _   | cycle | 4     |

| ZZ Active to sleep current                                                                                                                                                                                                            |                                                                                   | t <sub>zzi</sub>                                                                                                                                                                                          |     | 2   |     | 2   | cycle | 4     |

| ZZ Inactive to exit sleep current                                                                                                                                                                                                     |                                                                                   | t <sub>RZZI</sub>                                                                                                                                                                                         | 0   | _   | 0   | _   | cycle | 4     |

Notes: 1. Transition is measured ± 100 mV from steady-state voltage. This parameter is sampled.

- 2. A READ cycle is defined by WE HIGH for the required setup and hold times. A WRITE cycle is defined by WE LOW for the required setup and hold times.

- 3. This is a synchronous device. All address must meet the specified setup and hold times for all rising edges of CLK when chip enabled. All other Synchronous inputs must meet the setup and hold times with stable logic levels for all rising edges of clock (CLK) when chip is enabled. Chip enable must be valid at each rising edge of CLK to remain enabled.

- 4. Data-output is not guaranteed during the cycle when transition of ZZ from low to high occurs.

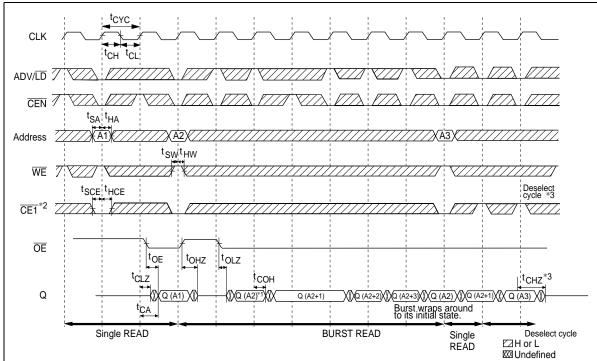

## **Timing Waveforms**

#### Read Cycle

Notes: 1. Q (A2) refers to output from address A2. Q (A2 + 1) refers to output from next internal burst address following A2.

- 2. CE3 and CE2 have timing identical to CE1. On this diagram, when CE1 is LOW, CE3 is LOW and CE2 is HIGH. When CE1 is HIGH, CE3 is HIGH and CE2 is LOW.

- 3. Outputs are disabled within one clock cycle after deselect.

- 4. ZZ is LOW.

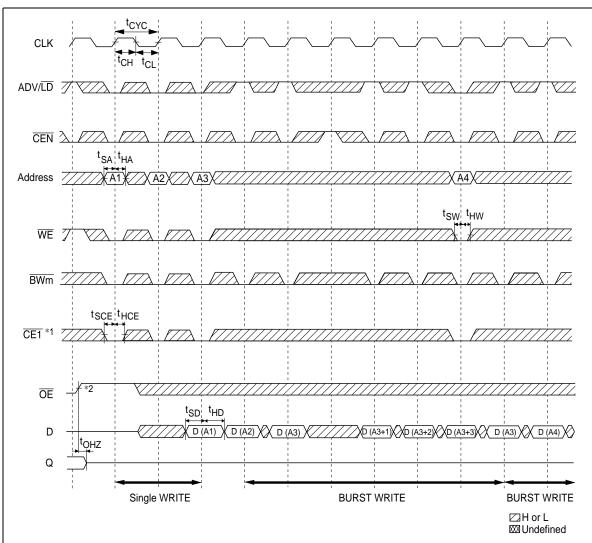

#### Write Cycle

Notes: 1.  $\overline{\text{CE3}}$  and  $\overline{\text{CE2}}$  have timing identical to  $\overline{\text{CE1}}$ . On this diagram, when  $\overline{\text{CE1}}$  is LOW,  $\overline{\text{CE3}}$  is LOW and CE2 is HIGH. When  $\overline{\text{CE1}}$  is HIGH,  $\overline{\text{CE3}}$  is HIGH and CE2 is LOW.

- 2. OE must be HIGH before the input data setup and held HIGH throughout the data hold time. This prevents input/output data contention for the time period prior to the byte write enable inputs being sampled.

- 3. Full width WRITE can be initiated by WE, BWa to BWd are LOW.

- 4. ZZ is LOW.

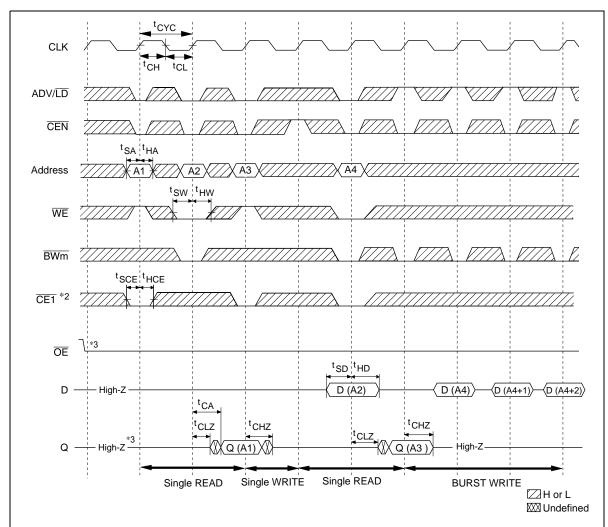

### Read-Write Cycle

Notes: 1. Q (A3) refers to output from address A3.

- 2.  $\overline{\text{CE3}}$  and CE2 have timing identical to  $\overline{\text{CE1}}$ . On this diagram, when  $\overline{\text{CE1}}$  is LOW,  $\overline{\text{CE3}}$  is LOW and CE2 is HIGH. When  $\overline{\text{CE1}}$  is HIGH,  $\overline{\text{CE3}}$  is HIGH and CE2 is LOW.

- 3. Timing is shown assuming that the device was not enabled before entering into this sequence. <del>OE</del> does not cause Q to be driven until after the following clock rising edge.

- 4. ZZ is LOW.

#### **Power-down State**

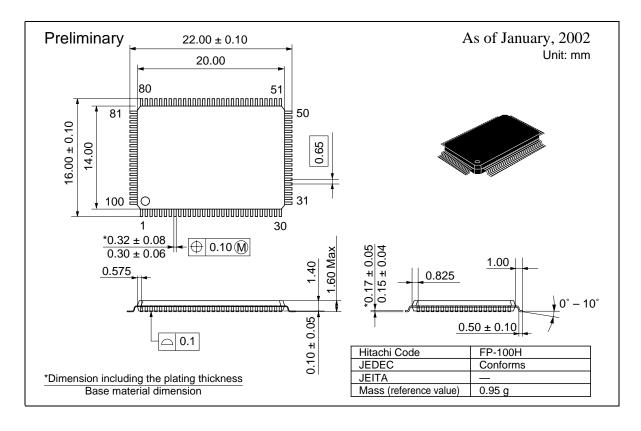

## **Package Dimensions**

#### HM66WP18512FP, HM66WP36256FP Series (FP-100H)

#### **Disclaimer**

- Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as failsafes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

Hitachi Asia Ltd.

#### Sales Offices

# IITACHI

Hitaci, Ltd.

Semiconductor Integrated Circuits Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: (03) 3270-2111 Fax: (03) 3270-5109

URL http://www.hitachisemiconductor.com/

#### For urter inormation rite to

Hitachi Semiconductor (America) Inc. 179 East Tasman Drive San Jose,CA 95134 Tel: <1 (408) 433-1990 Fax: <1(408) 433-0223

Hitachi Europe Ltd. Electronic Components Group Whitebrook Park Lower Cookham Road Maidenhead Berkshire SL6 8YA, United Kingdom Fax: <65-6538-6933/6538-3877 Tel: <44 (1628) 585000 Fax: <44 (1628) 585200

Hitachi Europe GmbH Electronic Components Group Dornacher Strae 3 D-85622 Feldkirchen

Postfach 201, D-85619 Feldkirchen Germany Tel: <49 (89) 9 9180-0 Fax: <49 (89) 9 29 30 00

Hitachi Tower 16 Collyer Quay 20-00 Singapore 049318 Tel: <65-6538-6533/6538-8577

URL: http://semiconductor.hitachi.com.sg

Hitachi Asia Ltd. (Taipei Branch Office) 4/F, No. 167, Tun Hwa North Road Hung-Kuo Building Taipei (105), Taiwan Tel: <886-(2)-2718-3666

Fax: <886-(2)-2718-8180 Telex: 23222 HAS-TP URL: http://www.hitachi.com.tw

Copyright Hitachi, Ltd., 2002. All rights reserved. Printed in Japan. Colophon 6.0

Hitachi Asia (Hong Kong) Ltd.

Harbour City, Canton Road

7/F., North Tower

World Finance Centre,

Tel: <852-2735-9218 Fax: <852-2730-0281

Group III (Electronic Components)

Tsim Sha Tsui, Kowloon Hong Kong

URL: http://semiconductor.hitachi.com.hk

Rev.0.4, Jun. 2002, page 22 of 22